内存标签上这串数字,暗藏了内存工作的“秘密”

2019-06-10 18:29IT之家 ()

一台电脑的性能怎么样,很多人会看处理器、显卡,而除了这两者,内存的重要性紧跟其后。内存也是我们平常接触最频繁的计算机硬件之一,它的容量的大小、频率的高低,与电脑运行的快慢有密切的关系。相信大部分消费者在购买内存时看且仅看容量、频率这两项参数。但事实上,影响内存性能的还有一项重要参数,就是内存时序。

那么什么是内存时序?这是小编在本文想和大家探讨的。我们暂且抛开定义,从内存的一些运行原理说起。

首先,内存是什么?内存是与CPU直接沟通的桥梁。打个比方,如果把CPU比作一个工厂,它是负责处理数据的。数据从哪里来?当然是从硬盘中来,所以硬盘相当于一个原料产地。

早期的电脑是没有内存的,CPU直接从硬盘中读取数据,就像工厂直接从原料产地采集数据原料。但是随着技术的发展,CPU工厂的处理能力极大提升,远远甩开了硬盘的运力,但是数据还是要从硬盘中读取啊,需要迁就硬盘的运力,所以CPU的发挥空间被大大限制了。

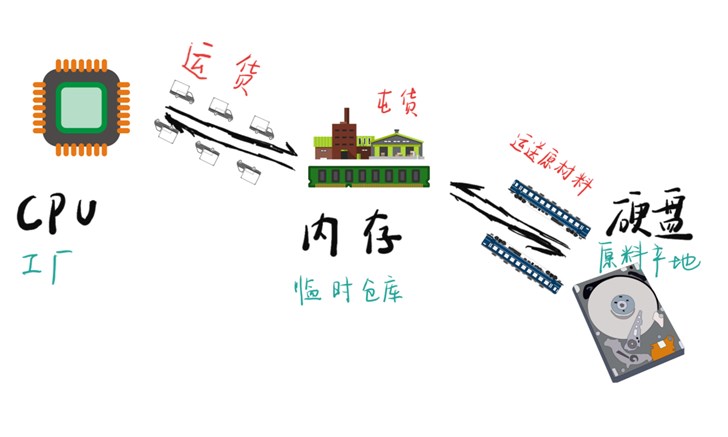

怎么办?这个时候,人们想到了一个方法——临时仓库。

你硬盘不是追不上CPU的速度吗?那就不让CPU直接找硬盘了,我们可以在工厂和原料产地之间设立一个前置的临时仓库,先屯一批货在仓库里,这个临时仓库,就是内存。

CPU需要数据,直接从临时仓库中读取,不再直接读取硬盘了。而这个临时仓库的运转速度是硬盘的几十倍不等,能够满足CPU处理速度的需要,所以它就会不断将CPU需要处理的数据预存在仓库里,这样,整个电脑的性能、效率都大大提高。

讲到这里,相信大家对这个临时仓库就很感兴趣了,很想走进仓库,看看它自己是怎么运转的,和工厂之间又是怎样工作的。

先说说临时仓和工厂之间是怎样沟通的吧。

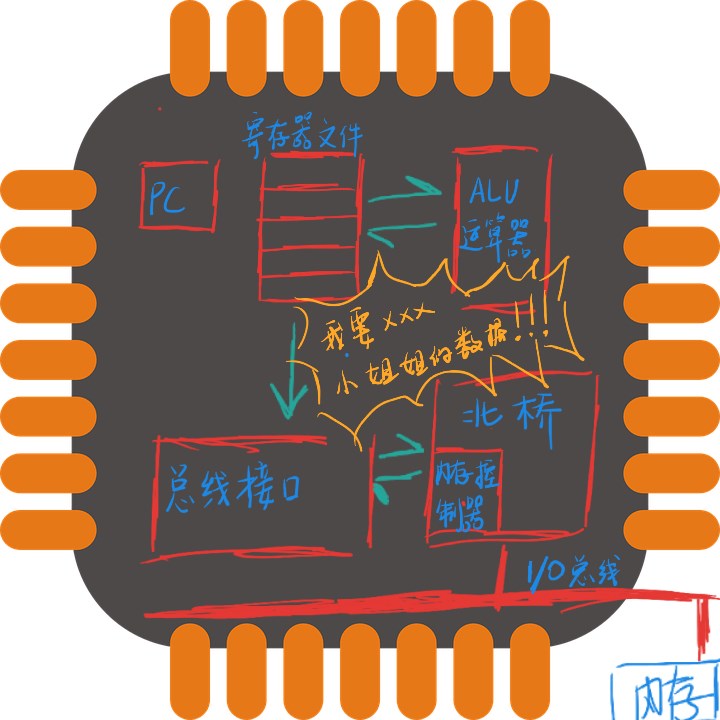

我们知道,在CPU里面,都有一个内存控制器,它就是工厂中负责和临时仓库直接沟通物流的窗口。

当CPU需要处理“XXX小姐姐”的数据,就大喊一声“我要XXX小姐姐的数据!”然后这条指令在工厂内部各个部门之间传递、转化,到达内存控制器,内存控制器负责和仓库沟通“XXX小姐姐”的数据在哪里。

插一句,具体工厂内部这个指令是怎么传递的,比较复杂。简单来说,指令首先会被传递到内存管理单元,在这里进行虚实转换,然后发往总线,总线再把命令传递给内存控制器,内存控制器接到命令后,对命令进行分析,了解自己的任务,然后找到临时仓库。

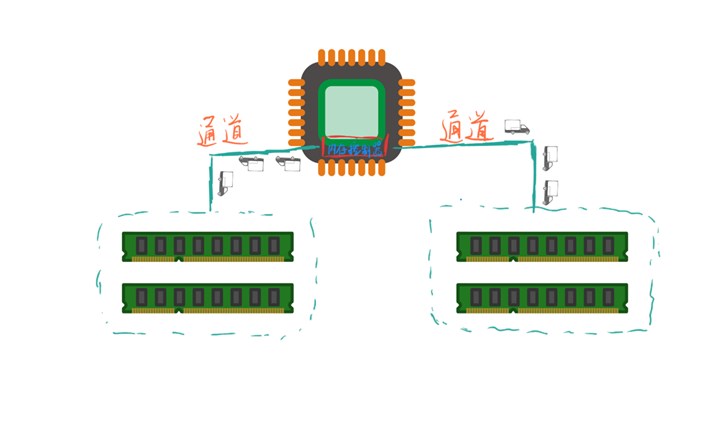

内存控制器和内存之间沟通的物流线路,就是内存通道(Channel)。很显然,这样的通道多多益善,毕竟多一条通道,就可以增加一倍的流通效率。不过,一个内存控制器只能控制一个内存通道,就目前消费级数据处理的需求来讲,两个通道基本也就足够了,当然也有三通道、四通道的,根据大家的需求和预算来吧。

顺着内存通道,就可以找到内存,也就是临时仓库了。那么这个临时仓库是什么样的呢?它是以怎样的方式存在?

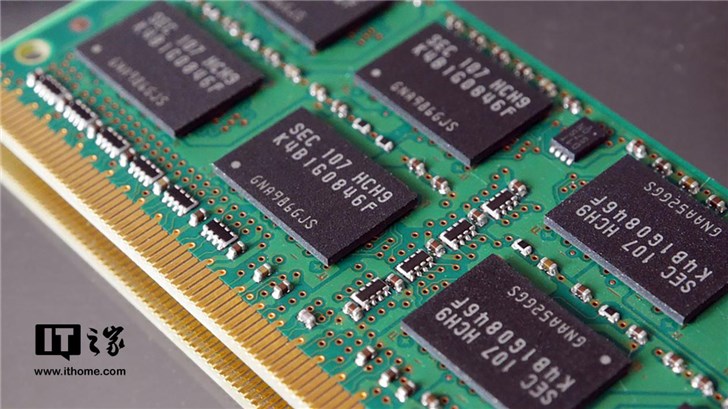

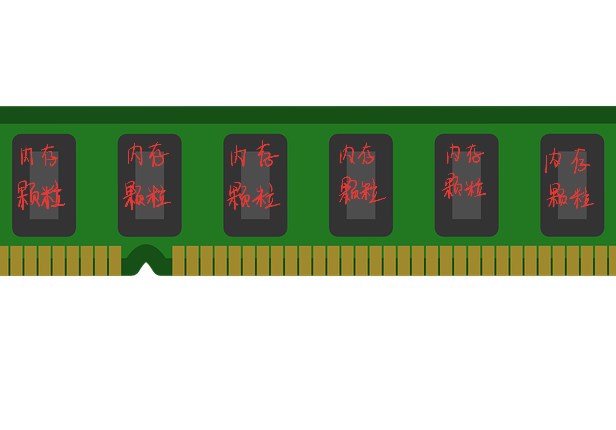

我们知道,数据是被存在内存颗粒里的,内存颗粒我们叫Chip。内存颗粒是内存的关键部件,就好像仓库里一个个库房,只不过打造这样的库房需要很高的技术,不是随便一个厂商都能生产出来的,毕竟它装载的货物非常独特,像三星、海力士等等,就是打造这样的库房的高手。

说起来,早期这个“临时仓库”是比较简陋的,直接以库房的形式存在,即内存颗粒是直接被插在主板上的,后来才被焊在一块模块化的电路板上,这个电路板,其实就是内存条。早期的叫SIMM,在内存发展进入SDRAM时代后,SIMM逐渐被DIMM取代。两者的区别和发展过程,这里就不方便展开啦。

这么说吧,现在来讲,DIMM就是内存条的基本形态,在上面打的比方中,其实就是临时仓库的实体形态。内存条上一排黑色的小芯片,就是内存颗粒(Chip),也就是库房。数据,就是从不同的库房里取出,然后发往CPU这个工厂的。很多时候,我们看到一个内存条上有8个内存颗粒,当然也有四个或者16个的,这是巧合吗?

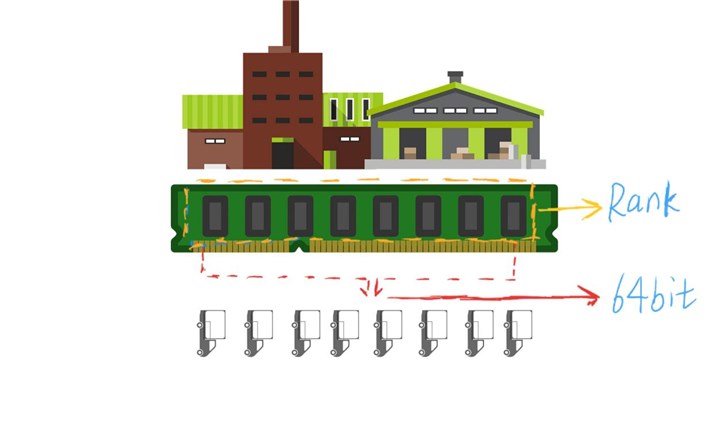

不是,这其实和CPU有关。我们刚才说到,内存控制器是CPU中和内存对接的窗口,而这个窗口的运力是有限制的。目前,内存控制器和内存对接的接口位宽主要是64 bit,也就是一个时钟周期里可以向内存发送或读取64 bit的数据,而一个内存颗粒的位宽比较小,有4 bit的,8 bit的,也有16 bit的,当少数也会有32 bit的,所以,实际应用时需要把多个内存颗粒并联起来,成为一个64 bit的集合,从而来满足CPU的运力要求。

而这样的一个集合,叫做Rank。目前绝大多数的内存条都有1个或者2个Rank。通常同种内存颗粒下,Rank数越多,可做的内存容量就越大。例如通常我们在内存条上会看到1R×8或者2R×8的参数,其中R就代表Rank,8代表内存颗粒的位宽为8bit。1R×8代表这个DIMM上有1×(64÷8)=8个内存颗粒,2R×8代表这个DIMM上有2×(64÷8)=16个内存颗粒。注意,CPU一次只能对一个Rank进行访问和操作。

OK,我们想象一下,在这个内存这个临时仓库中,有一排(1个Rank)的库房(内存颗粒),它们负责与不远处的工厂(CPU)沟通、运输原材料(数据)。接下来,就该研究一下工厂到底是怎样和这些库房沟通的了,工厂想要哪些数据?这些数据在哪里取?这些总该弄清楚吧。

这就涉及到一个关键的步骤了:寻址。

前面我们说到当CPU喊出“我要XXX小姐姐的数据”时,其实发出的本质上是一个地址指令,根据这条地址在内存中可以找到对应的数据。再看内存这里,刚才我们已经讲到了库房,也就是内存颗粒了,数据就储藏在里面。干过仓储工作的人都知道,库房里的货物不是随便摆放的,需要遵循一定的排列体系。内存颗粒也是一样,所以我们接下来要看一下里面数据存取的逻辑结构,看看这个“库房”里的“货物”是怎样摆放的。

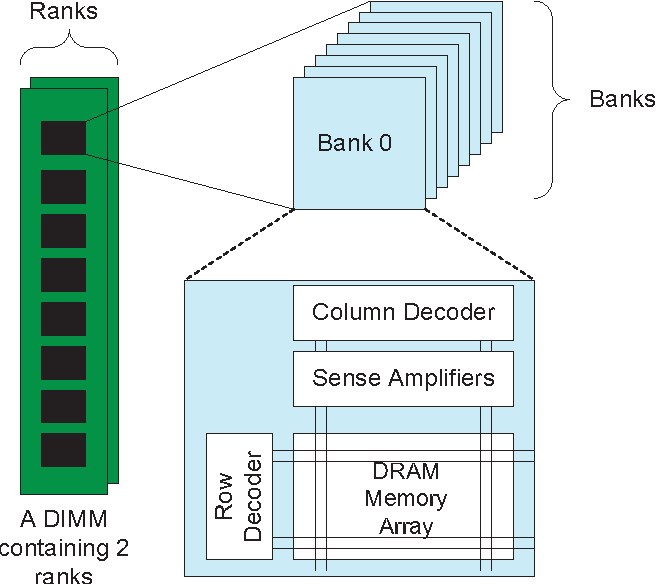

前面我们讲到的最小单元是Chip,也就是库房,现在我们走进这个库房里,你会看到库房里排列着一排一排的货架,而每一个货架中,有一个一个整齐划一的小方格抽屉组成的阵列,而货物,就分别放在这些小方格抽屉里。

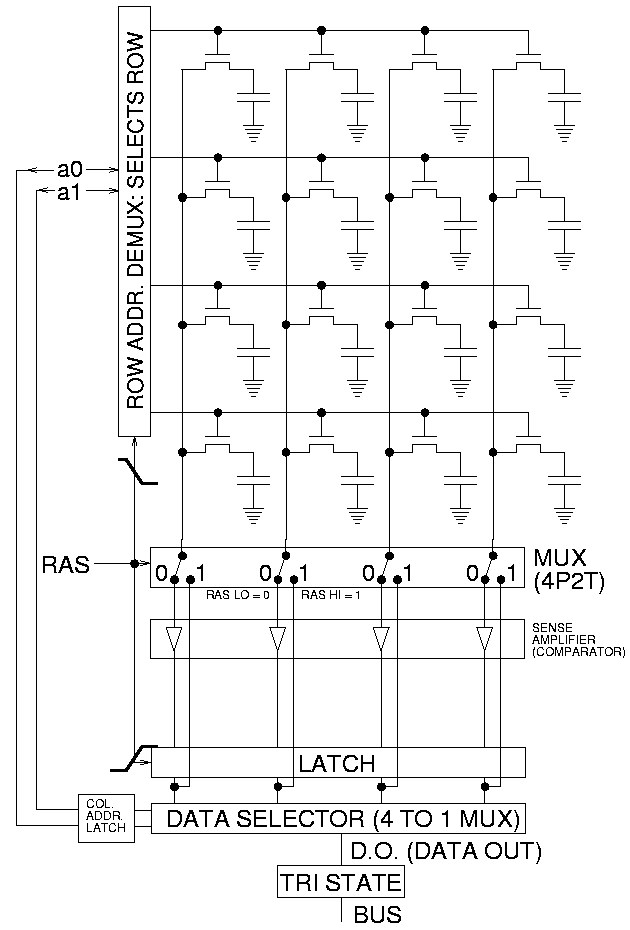

初中我们就学过坐标系,OK,如果我们将这些小方格抽屉组成的阵列按照横轴和纵轴进行编号,那么每一个方格抽屉就有了自己的坐标,这样,拿货的时候就可以精确定位到每一个方格抽屉了。

这就是内存颗粒内部存取数据的逻辑。当然,你可能会问,为什么内存颗粒内部存取数据的逻辑要是这样的呢?这个解释起来相当复杂,简单来回答,主要是从降低成本的角度来考虑的,DRAM设计的目标之一就是降低晶体管使用的成本。

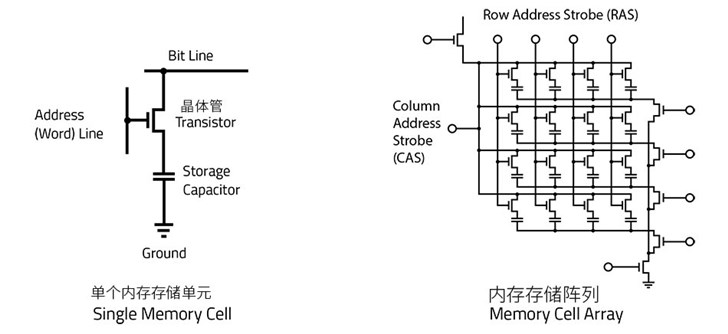

在内存颗粒内部,晶体管充放电时,电压和电荷需要管理,这个管理单元叫做Sense Amplifier(传感放大器),这种传感放大器本身由更多的晶体管组成,成本较高,所以在设计的时候,需要尽可能减少传感放大器,所以一个晶体管对应一个传感放大器就别想了,太高成本。科学家发现,当晶体管形成方格阵列时,就可以在不影响稳定性的前提下最大程度减少传感放大器的数量,所以,我们就能看到内存颗粒内部为由最小存储单元组成的存储阵列。

在内存中,这样的一个存储整列,我们把它称作一个逻辑Bank(L-Bank)或者直接叫做Bank,这一个Bank也就是我们前面说的货架。一个内存颗粒中,由多个Bank组成,具体有多少个Bank,这并非固定的,而是随着内存技术的发展而变化的。

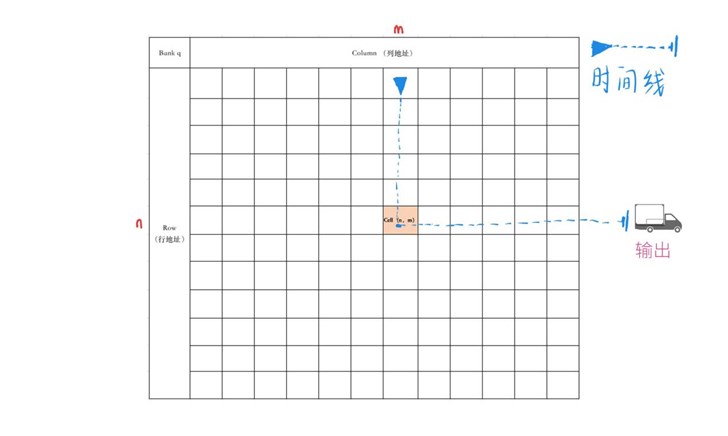

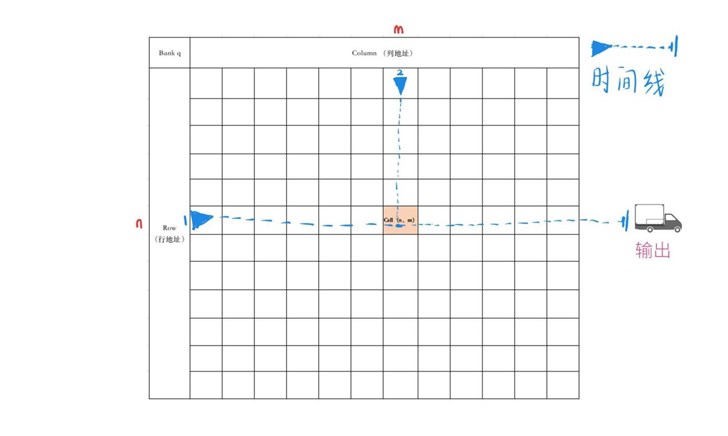

再来看单一的Bank,其中我们刚才所说的最小存储单元,也就是一个方格抽屉,被称作“Cell”,它能存储的数据量,其实也就是内存颗粒的位宽。精确定位到这一个方格,很容易,我们只需要知道它在哪一个Bank的第几行(Row)第几列(Column)。

这就是寻址的过程。

有了这个做基础,接下来,我们终于要讲到内存时序了。

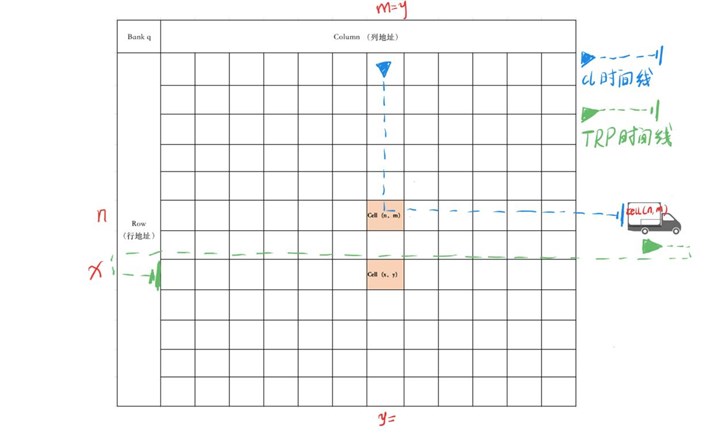

以小编手上的这条内存为例,在它的标签上,有这样一组参数:CL 16-18-18-38。这一串数字,其实就是内存时序(不同的内存有不同的内存时序)。而这四个数据,对应四个性能参数,他们分别是CL、TRCD、TRP和TRAS。对于这四个参数,我们未必需要了解它们对应的学名,但是需要知道他们分别表达什么意思。

首先是CL,它的意思是发送一个列地址到内存与数据开始响应之间时延。这是从已经打开正确行的DRAM读取第一比特内存所需的周期数。也就是说,当我们要找到一个数据时,确定在哪个Bank后,然后确定在哪一行,再确定在哪一列。

用之前的例子来说明,就是CPU工厂发出指令,包含行地址和列地址等信息,假设是在第q个货架的第n行第m列。临时仓库接到信息后,先派工作人员找到对应库房的第q个货架旁,找到这个数据(货物)所在的第n行,然后再看货物所在的第m列。注意,从你开始找第m列的那一刻开始,到这个货物被找到,并被运输出仓库,这个过程需要的时间,就是CL时延。显然,我们希望这个数字越小越好。

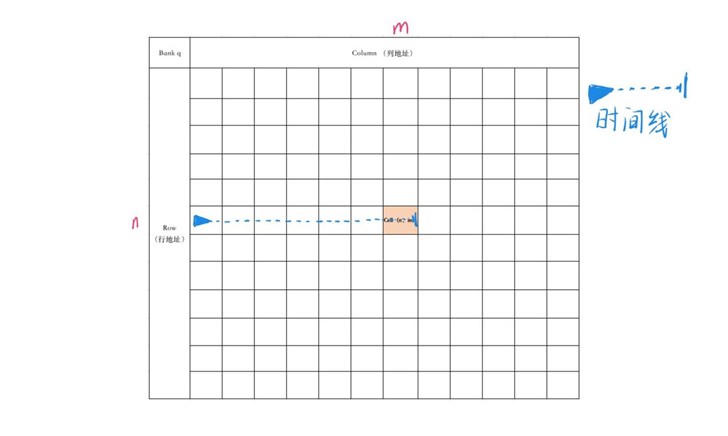

第二个数字TRCD,意思打开一行内存并访问其中的列所需的最小时延。这个很好理解。上面说的CL时延,是从你开始找第m列开始的,但是在这之前,你确定了货物所在的第n行,然后开始找其中的第m列,这两个行为之间,也是需要间隔的,这个间隔的时间,就是TRCD时延。

TRP是第三个数字,意思是发出预充电命令与打开下一行之间所需的最小时钟周期数。我们接着用上面的例子来说明。CPU工厂发出指令,不会一次只要一个货物(数据),前面我们说过,是64bit的数据,所以工作人员在找到第一个货物的时候,还要接着找下一个货物。当然,找的方法和上一个一样,还是先从行开始定位。

但是,工作人员在找到上一个货物和开始找下一个货物之间,总是需要先休息一会。这个休息的时间在内存里叫做预充电。TRP时延就是从发出预充电指令,到开始找下一个货物的第n行,这个过程需要的时间。

最后一个数字是TRAS,它的解释是行活动命令与发出预充电命令之间所需的最小时延。我们仍然用上面的这个例子通俗去理解。其实这个数字,表达的就是一个总时间。是什么总时间呢?就是当工作人员找到第q个货架第n行开始,到系统发出预充电,即工作人员开始休息这个过程的总时间,不严谨地说,它就是CL+TRCD的时间之和,当然,在实际内存模块中,数字上并不是绝对的。

当对每个数字进行解释分析之后,相信大家也就了解内存时序这个参数所代表的含义了。客观上讲,我们希望内存时序的这一串数字都是越小越快,数字越小,代表时延越小,时延越小,说明内存运行的速度越快。

通常,内存时序中的第一个数字,也就是CL的参数是最重要的,很多厂商甚至也会在内存产品标签中单独标注CL的值,因为这个数字告诉我们要等待多少个时钟周期后才能拿到数据。

购买小建议:

介绍完了内存时序,相信大家也对内存内部的工作原理有了一个大概的了解。不过这里要说的是,内存时序并不是决定内存性能最关键的数据,这只是影响内存性能的重要因素之一。我们不能说内存时序更低,内存的性能就一定强,或者内存时序高,内存的性能就一定弱,因为我们不能抛开内存的标准和频率来孤立地看内存时序。

举个例子,如果一块DDR3的实际频率是800MHz。那么它的周期时间就是1/800MHz=1/(800×10^6Hz)=0.00125μs/周期=1.25ns/周期,我们假定CL都是10,那么这块内存的实际延迟就是12.5ns。

而我们再找一块实际频率更高的DDR3内存,为1600MHz,按照刚才的算法,周期时间就是0.625ns/周期,那么实际延迟就是6.25ns。显然,这个延迟是要比CL同为10的上一款内存更短,即便我们假设这款内存的CL是12,那么它的延迟也只有7.5ns。

所以,内存时序和频率等参数都不是孤立来考察的,如果你对内存有非常严苛的要求,或者用于发烧级的场景,那么在看了它的标准、频率后,也需要考察其内存时序,而如果你只是普通用户,那么通常优先考察频率是没问题的,因为它对内存性能的影响更大。当然,通常情况下,高频率、低内存时序的内存,性能自然也是更好的。

评论已关闭!